Proje Ortakları

Müşteri Kuruluş: Procenne – Güvenpark Bilişim Teknolojileri Ar-Ge Tic. Ltd. Şti.

Yürütücü Kuruluş: İstanbul Teknik Üniversitesi, Gömülü Sistem Tasarımı Laboratuvarı

Destekleyen Kuruluş: TÜBİTAK 1505 Üniversite-Sanayi İşbirliği Destek Programı

Proje Ekibi

Yürütücü: Prof. Dr. Berna Örs Yalçın

Bursiyer: — İLAN

Proje Kısa Tanıtımı

HSM’ler kriptografi algoritmalarının yüksek performansla ve güvenli şekilde donanımsal olarak gerçeklenmesine olanak sağlarlar. Özellikle finans, askeriye, istihbarat, sağlık, v.b. sektörlerde kritik görevler üstlenen ve büyük veri genişlikleri ile çalışan güvenlik protokollerinin yüksek hızda çalışma gereksiniminin karşılanabilmesi algoritmaya özel donanımlarla (Custom IP) mümkün olabilmektedir. Kriptografi algoritmaları için ASIC olarak veya FPGA üzerinde gerçeklenen Custom IPler her ne kadar algoritmaların yazılım gerçeklemelerine göre çok daha hızlı çalışsalar da kontrol ve dış dünya ile veri haberleşmesinden sorumlu bir işlemci kullanılmakta ve Custom IPler bu işlemciye bağlanarak SoC oluşturulmaktadır.

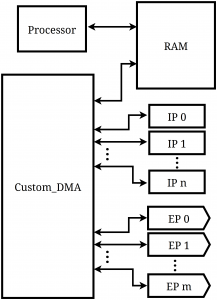

Kriptografi algortimalarının gerektirdiği veri girişleri ve çıkışları günümüzde var olan işlemcilerin veri yolu uzunluklarına göre 4 ila 128 kat daha uzun olduklarından, doğrudan işlemciye bağlanan Custom IPler ile bir sistem oluşturulduğunda zamanının çoğu veri aktarımına ayrılacağından sistem verimli çalışmayacaktır. Bu projede, RISCV işlemcisinin sadece RAM arayüzü kullanılarak PCIe gibi veri portları, Custom IP ve işlemci arasında RAM üzerinden komutların ve verinin iletimini sağlayacak özel bir doğrudan bellek erişim modülü tasarlanacaktır. Tasarlanan bu modül kullanılarak; yüksek hızlı bir HSM SoC olarak FPGA üzerinde gerçeklenecek, fonsiyonel ve performans testlerin ve ayrıntılı doğrulaması yapılacak ve ASIC tasarımı, üretimi ve testleri ile proje son bulacaktır.

Yöntem

Özel doğrudan bellek erişim modülü (ÖDBEM) tasarımı yapılırken mevcut Custom DMA (Direct Memory Access) tasarımları incelenecek, literatürde benzer problemler için uygulanmış çözümler araştırılacaktır. Tasarlanacak özel doğrudan bellek erişim bloğunun hedeflenen davranışları sağlayabilmesi ve performansı artıracak yeni özellikleri de içerecek bir mimari, literatür araştırmasının ardından netleştirilecektir. Tasarımın esnek, geliştirmelere açık, gerçeklemesi ve kullanımı kolay olmasına önem verilecektir.

İşlemci, algoritmaya özel donanımlar (Custom IP) ve bellekten oluşan bir kırmık üstü sistem (System on Chip, SoC), veri haberleşmesinden kaynaklanan performans kaybını azaltacak şekilde tasarlanacaktır. Ayrıca sistemin dış dünya ile Ethernet, UART, PCI gibi standart arayüzler üzerinden haberleşme imkanı sağlayan harici arayüzler (External Ports, EP) içermesi planlanmaktadır. Bu arayüzler ile bellek arasında haberleşme yine bu projede tasarlanacak olan özel doğrudan bellek erişim bloğu ile sağlanacaktır. Böylece dış dünya ile haberleşmek için de işlemci üzerinde herhangi bir işlem yükü olmayacak şekilde tasarım yapılacaktır.

- Kırmık Üstü Sistem Tasarımı: Zynq işlemcisi, Direct Memory Access Bloğu, kriptografi çekirdekleri, PCIe arayüzü kullanılarak kırmık üstü sistem tasarlanması yapılacaktır. Tüm veri transfer işlemlerini içerecek şekilde testler yapılacak ve test dosyası kullanılarak davranışsal benzetim yapılacaktır. Analiz aşamasında belirlenen performans isterlerine göre kırmık üstü sistem gerçeklenecek ve FPGA’e yüklenecektir. FPGA üzerinde bellek erişim hızlarını test etmek üzere programın yazılacak ve performans kısıtlarının sağlanıp sağlanmadığı test edilecektir.

- Özel Doğrudan Bellek Erişimi Tasarımı: RISCV işlemcisi, kriptografi çekirdekleri, PCIe ve BRAM arayüzlerinin gösterildiği sistem şemasının çizilmesi, sistemin sağlaması gereken davranışlar gibi hedeflenen fonksiyonel özellikler belirlenecektir. Analiz aşamasında belirlenen haberleşme hızı kısıtına bağlı olarak kullanılabilecek giriş çıkış arayüzleri gözden geçirilerek, kısıtları sağlama ihtimali olanların tasarımda denenmesi yapılacaktır. Hız kısıtını sağlayacak şekilde olabildiğince düşük kaynak tüketimine sahip olan blok diyagramı belirlenecek.

- Özel Doğrudan Bellek Erişimi ile Haberleşen Kırmık Üstü Sistemin Tasarlanması: Açık kaynak kodlu bir RISCV işlemci, performans ve alan tüketimi en optimal olan tasarım projede kullanmak üzere belirlenir. RISCV işlemcisinde var olan arayüzlerle haberleşecek IP Üretilir. Kırmık üstü sistemin blok tasarımı yapılır, özel doğrudan bellek erişimi tasarımı için sürücü yazılır, tasarlanan sistemin VHDL kodunun oluşturulur, davranışsal benzetim yapılır, sentez ve gerçekleme yapılır, sentez sonrası benzetimin yapılır. Bütün benzetimler sonunda elde edilen tasarımın FPGA programlama dosyası olan “bitstream” üretilir ve FPGA’de programlanarak kırmık üstü sistem FPGA’e yüklenir.

- Fonksiyonel Doğrulama ve Performans Testleri: Sistemin test edilmesi için test vektörleri oluşturulur ve PC’den FPGA’e bir haberleşme protokolü kullanılarak gönderilir ve aynı şekilde FPGA’den gelen cevaplar PC tarafından okunarak sonuçların karşılaştırması yapılır. Bir hata tespit edilmesi durumunda hatanın nedeni araştırılır, bulunur, hata giderilir, test adımları tekrar edilir. Performans testleri için test planı doğrultusunda test dosyası oluşturulur ve dosya çalıştırılarak sistem test edilir ve davranışların her biri için ayrı ayrı performans sonuçları belirlenir.

- Doğrulaması tamamlanan SoC ASIC olarak gerçeklenecek, ürettirilecek ve PCB üzerinde testleri gerçeklenecektir.